描述:

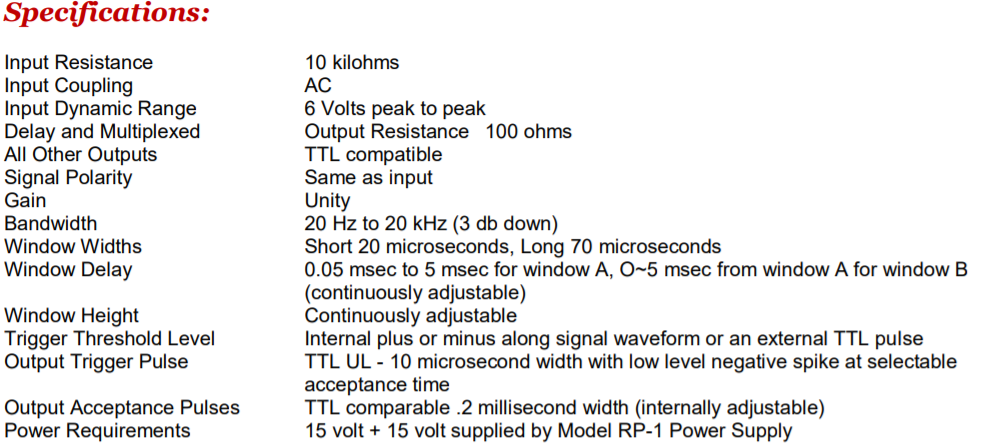

DDIS-l模型在時(shí)間和振幅上產(chǎn)生兩個(gè)窗口。窗口可以在高度、高于或低于基線以及在時(shí)間上的任何地方進(jìn)行調(diào)整,對(duì)于窗口a,在觸發(fā)點(diǎn)之后最多5毫秒,對(duì)于窗口B,在距離窗口a最多5毫秒。

觸發(fā)點(diǎn)由用于正斜率或負(fù)斜率檢測(cè)的連續(xù)可調(diào)水平控制設(shè)置。信號(hào)和所有窗口電平被多路復(fù)用,因此只需要示波器的一個(gè)通道。多路復(fù)用消除了對(duì)示波器電平漂移的調(diào)整;此外,不需要z軸強(qiáng)化。DDIS-1內(nèi)置了一個(gè)具有X1和X2延遲能力的模擬延遲電路,使該單元成為完整的尖峰識(shí)別系統(tǒng)。

可以在查看輸入到單元的原始數(shù)據(jù)時(shí)設(shè)置初始觸發(fā)閾值。然后,信號(hào)在進(jìn)入多路復(fù)用輸出電路之前通過(guò)Xl模擬延遲,以便在設(shè)置判別參數(shù)時(shí)可以查看整個(gè)波形。在“delay OUT”(延遲輸出)輸出處提供額外的X2延遲,因此接受脈沖可以觸發(fā)額外的示波器,該示波器仍將查看整個(gè)波形,從而對(duì)所識(shí)別的尖峰進(jìn)行視覺(jué)確認(rèn)。

提供一個(gè)“選擇AC”開(kāi)關(guān),將觸發(fā)輸出線上作為低振幅負(fù)尖峰的任何接受脈沖輸出與正TTL觸發(fā)脈沖多路復(fù)用,以便通過(guò)調(diào)整示波器觸發(fā)電平從觸發(fā)脈沖或接受脈沖快速觸發(fā)CRT。接受脈沖不變。DDIS-l型采用模塊化結(jié)構(gòu),可輕松滑入RP-l型機(jī)架安裝電源模塊籠式系統(tǒng)。